Использование IP Gowin для BSRAM

Для того, чтобы использовать BSRAM, можно взять готовые компоненты, называемые IP, которые предоставляют вендоры. В нашем случае, это компания Gowin.

Создадим же модуль с однопортовой bsram.

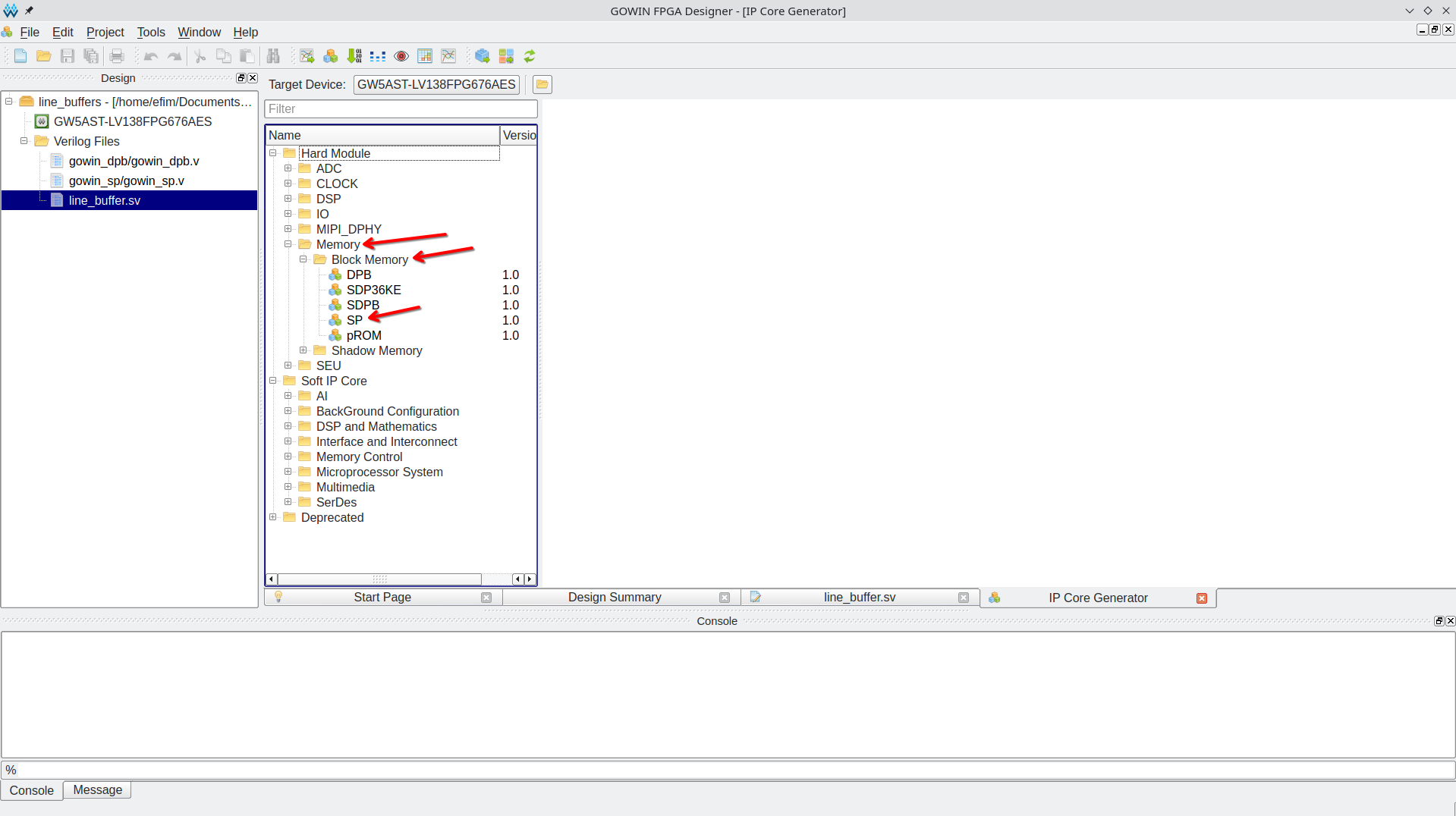

Для этого в ide нужно нажать на значок с тремя кубиками на верхней панели (или Tools → IP Core Generator).

После чего откроется меню для выбора нужного IP (здесь же есть ссылки на документацию к разным IP, если нажать один раз). Нас интересует память, так что выбираем соответствующий модуль (Memory → Block Memory → SP (от Single Port)).

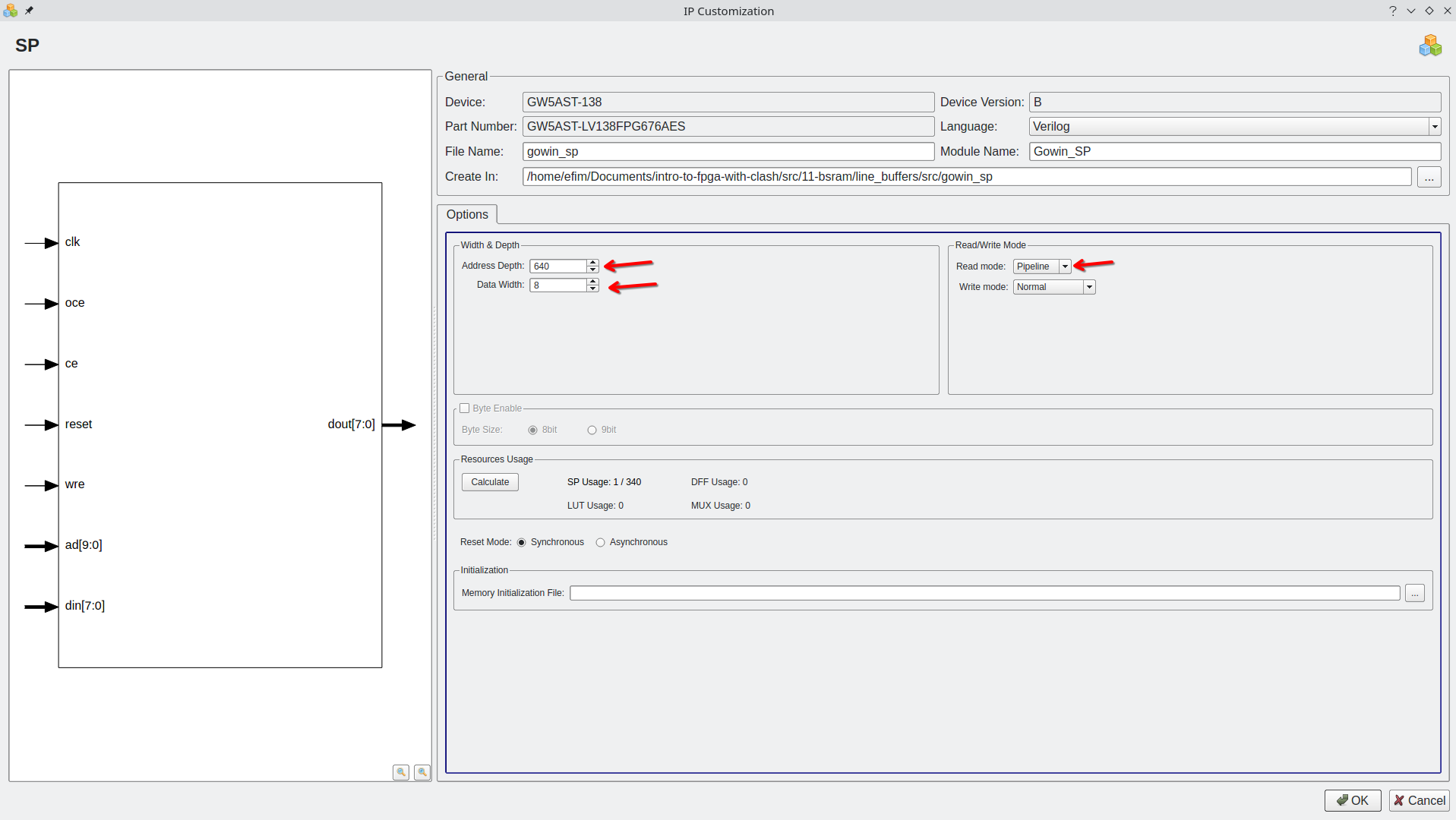

Кликнув дважды, вам откроется меню для конфигурации модуля с памятью. Слева показана схема итогового модуля, а справа настройки. По умолчанию общие настройки будут для вашей платы, там вы можете поменять и папку, в которой будет лежать сконфигурированный модуль. Самыми интересными для нас параметрами (более подробно про которые можно прочитать в UG300E) являются:

-

Address Depth — это количество адресуемых ячеек памяти. Для наших целей считаем, что это ширина изображения — 640 пикселей, так что выставляем 640.

-

Data Width — количество бит для одной ячейки. В нашем случае это один байт.

-

Read mode — режим чтения: будет ли использоваться дополнительный регистр для чтения (bypass — не будет; pipeline — будет). Это влияет на задержку в один такт для чтения. При выборе bypass мы будем меньше думать о задержках, но снизим себе максимальную частоту схемы. Выбираем pipeline.

После этого, в соответствующей папке появится модуль с сконфигурированным под наши нужды IP. Если на него внимательно посмотреть, то можно заметить несколько вещей

-

Тут нет никакой магии, этот модуль можно было бы написать и руками.

-

Он использует другой модуль SP. Соответственно, надо позаботиться о том, чтобы симулятор его видел. Для этого нужно iverilog-у прописывать путь к реализованным IP. У нас это

$FPGA_TOOLS/simlib/gw1n/prim_sim.v. -

У него довольно сложный интерфейс, в котором нужно разобраться. Описание портов есть в документации или, для нашей конфигурации, в табличке ниже.

| Название порта | Вход/Выход | Описание |

|---|---|---|

din[7:0] |

Вход |

Входной сигнал данных |

dout[7:0] |

Выход |

Выходной сигнал данных (совпадает по типу с входным) |

ad[9:0] |

Вход |

Адрес, по которому происходит чтение/запись |

wre |

Вход |

Сигнал разрешения записи: |

ce |

Вход |

Тактовый разрешающий сигнал.

При |

clk |

Вход |

Тактовый сигнал |

reset |

Вход |

Сигнал сброса. Поддерживает синхронный и асинхронный сброс. Сбрасывает управляющие регистры, но не данные в памяти |

oce |

Вход |

Сигнал разрешения вывода данных (только для Pipeline-режима): Не используется в Bypass-режиме. |